Reti sequenziali

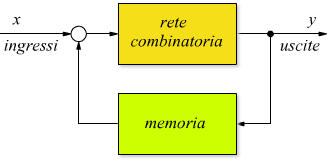

Nelle reti combinatorie, il valore dell'uscita dipende esclusivamente

dal valore assunto dagli ingressi in quel dato istante.

Nelle reti sequenziali, il valore dell'uscita non dipende solo dal valore

assunto dagli ingressi in un dato istante, ma anche dai livelli logici assunti

dalle uscite negli istanti precedenti. Si può dire che nelle reti combinatorie

il valore dell'uscita non dipende dal tempo, mentre nelle reti sequenziali

la variabile tempo riveste una grande importanza.

Se in un determinato istante tn gli ingressi e le uscite si trovano

in un determinato stato, è possibile che nell'istante successivo tn+1

una variazione dei valori logici di ingresso determini un nuovo stato delle

uscite. Se lo stato delle uscite dipende, sia dallo stato degli ingressi

al tempo tn+1 sia da quello delle uscite all'istante precedente

tn , allora, si può dire che il circuito è in grado di conservare

memoria della sequenza degli stati assunti dagli ingressi e dalle uscite.

Le strutture circuitali che possono realizzare queste funzionalità di memoria

sono molteplici, ma sono tutte caratterizzate da un collegamento di reazione

(feedback) che riporta in ingresso lo stato delle uscite.

Anche il modo in cui vengono effettuate le variazioni in ingresso possono

cambiare.

Nel caso del latch, la semplice variazione in ingresso determina una variazione

dell'uscita. In alcune configurazioni come il latch con abilitazione il

circuito accetta la variazione degli ingressi solo se l'ingresso supplementare

di abilitazione è attivato.

In altri casi, come il flip-flop è invece presente un segnale di cadenza

(clock) in corrispondenza del quale vengono scansionati (triggerati) gli

ingressi e soltanto in corrispondenza di tale controllo avvengono le eventuali

variazioni delle uscite.

Questi dispositivi rappresentano gli elementi minimi per memorizzare un

bit (0 o 1) e possono essere usati per costruire reti sequenziali più complesse,

come contatori, registri ed automi.

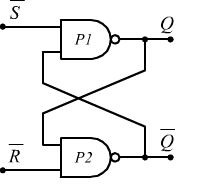

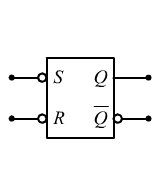

Latch SR

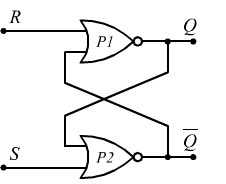

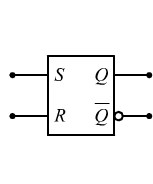

Il circuito disegnato è un latch realizzato con due porte NOR e i due

ingressi S (set=impostare) ed R (reset=azzerare) e i due terminali di uscita

Q e del suo complementare Q.

Nel circuito si notano i collegamenti di reazione incrociata tra l'uscita

Q e l'ingresso della porta P2 e tra l'uscita Q e

l'ingresso di P1.

Quando gli ingressi vengono attivati attraverso opportuni livelli logici,

l'uscita Q e di conseguenza la sua complementare Q

possono essere portate in uno dei due stati 0 o 1, nei quali può rimanere

stabilmente anche quando gli ingressi vengono disattivati.

Si tratta di un dispositivo bistabile, cioè dotato di due stati stabili

nei quali può rimanere bloccato (latch=chiavistello) e mantenere (memorizzare)

un bit.

Per capire come funziona il circuito, basta osservare cosa può succedere a secondo degli ingressi che vengono attivati.

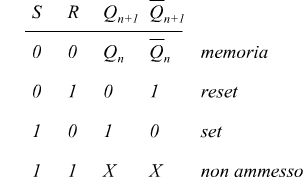

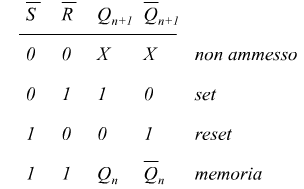

S=R=0 . In questo caso le uscite delle

porte NOR non dipendono dagli ingressi, ma da Q e Q.

Le porte NOR si comportano come invertitori; se per esempio Q=0 → Q=1

e viceversa se Q=1 → Q=0.

La condizione S=R=0 causa una condizione di mantenimento delle uscite cioè

di memorizzazione dei valori logici precedentemente assunti.

S=0 ed R=1 .La porta P1 ricevendo in ingresso un 1 , commuta la sua uscita; la porta P2, a sua volta, avendo in ingresso S=0 e Q=0 assume in uscita il livello logico Q=1. Lo stato di ingresso S=0 ed R=1 determina una situazione di azzeramento dell'uscita Q.

S=1 ed R=0 . L'uscita della porta P2, che riceve in ingresso un 1, diventa o rimane Q=0, di conseguenza l'uscita di P1, avendo entrambi gli ingressi a 0 commuta a livello logico 1. La condizione S=1 ed R=0 che ha come ingresso attivo S (set=imposta) metre R è inattivo, provoca l'impostazione dello stato logico 1 sull'uscita Q.

S=R=1 . L'ultima condizione possibile

comporta una situazione di ambiguità ed è inutilizzabile.

Se, infatti, poniamo S=R=1, entrambe le uscite sarebbero forzate a livello

logico 0. Questo fatto è contrario all'asserimento che Q e Q

siano complementari tra di loro e questo può portare e gravi inconvenienti.

Supponiamo, infatti che gli ingressi, dopo essere rimasti entrambi ad 1

, vengano portati entrambi a 0 in modo che il latch venga a trovarsi nella

condizione di memoria; dato che non si può immaginare una commutazione istantanea

delle porte non sarà possibile prevedere quale potrebbe essere lo stato

finale delle uscite.

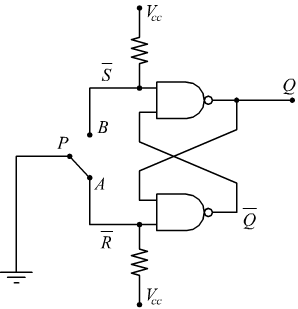

Latch SR a porte NAND

E' possibile costruire il latch anche con le porte NAND. La verifica dell'operativita di questo dispositivo può essere fatta in modo analogo a quanto visto per il latch a porte NOR; bisogna notare però, che in questo caso gli ingressi sono attivi bassi (S ed R).

Infatti per ottenere, ad esempio, la condizione di reset occorre attivare R portandolo a 0. Lo stato di memoria. quindi lo stato inattivo di riposo è stavolta abbinato ai livelli logici di ingresso S=R=1; in questa condizione, infatti, P1 e P2 invertono gli stati presenti sugli ingressi di reazione e quindi mantengono le uscite nello stato precedente. Applicando agli ingressi lo stato logico 0, la situazione sulle uscite diventa Q=Q=1: questo stato di ambiguità dove il valore dell'uscita è uguale a quello della sua complementare non deve pertanto essere usato.

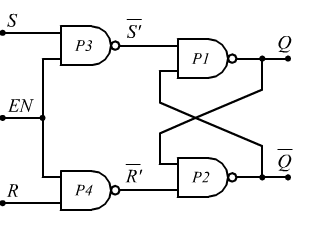

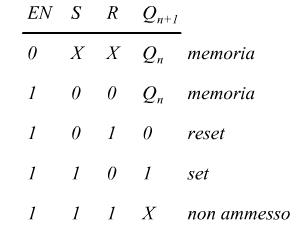

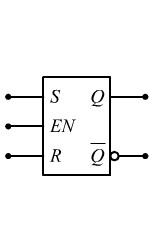

Latch con abilitazione

Nel circuito seguente, oltre agli ingressi dati è presente un ingresso supplementare EN (enable=abilitazione) che controlla il funzionamento del latch.

Quando EN=0 le porte di controllo P3 e P4 sono entrambe disabilitate con

le uscite S'=R'=1 mantengono

il latch in stato di memoria.

Il latch è in questa circostanza virtualmente isolato dalla sorgente dei

dati ed è insensibile ad eventuali variazioni dello stato di S ed R. Quando

EN=1 si ha S'=S ed R'=R

in questo modo i terminali S ed R del circuito, vengono di fatto ad essere

ingressi attivi alti di set e reset del latch.

Si comprende come le porte di isolamento funzionino da invertitori per gli ingressi S ed R. Nella tabella della verità del dispositivo il simbolo × esprime una condizione di indifferenza, indicando in questo modo che gli ingressi S ed R possono valere 0 o 1 indifferentemente: la condizione EN=0 pone in ogni caso il latch in uno stato di memoria.

Anche in questo caso lo stato S=R=1 non può essere usato per il fatto che portano le uscite Q e Q allo stato 1, il che implica la presenza di un valore non predicibile in uscita appena S o R ritornano a 0.

Il latch con abilitazione è anche denominato latch SR gated o strobed latch in quanto l'ingresso di abilitazione EN è spesso chiamato ingresso di strobe. L'intero dispositivo è talvolta anche denominato latch dinamico per distinguerlo dai semplici latch non dotati di porte di isolamento che invece vengono denominati latch statici.

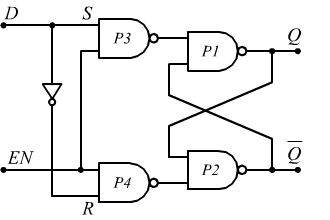

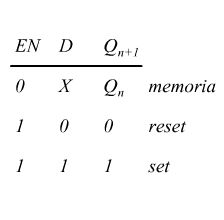

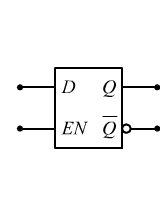

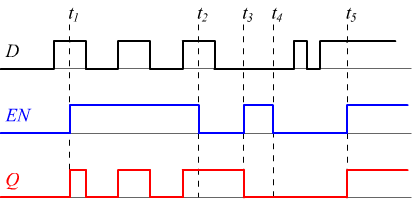

Latch di tipo D

Questo dipositivo, derivato dal latch dinamico, è anche chiamato latch

D gated. In esso viene introdotta una modifica che consente di utilizzare

un solo ingresso dati (D). La porta NOT posta tra gli ingressi S ed R fa

in modo che sia sempre D=S=R. In questa maniera

le configurazioni di ingresso possibili sono soltanto

D=S=0 con R=1

D=S=1 con R=0

Se EN=1 la prima delle due configurazioni (D=0) pone il latch in uno stato

di reset (Q=0) mentre la seconda (D=1) lo pone in stato di set (Q=1).

Pertanto se EN=1 il latch è trasparente rispetto al dato posto su D e l'uscita

Q segue l'ingresso D. Se invece EN=0 le porte di controllo sono disabilitate

e il latch conserva il dato memorizzato in precedenza, prima della disabilitazione.

Il diagramma temporale del funzionamento di un latch di tipo D è mostrato qui di seguito.

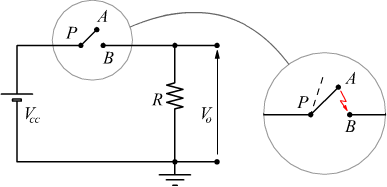

Circuito antirimbalzo

Un impiego tipico del latch SR è quello di elemento interruttore.

Il suo compito è quello di di produrre una chiusura o un'apertura del circuito,

sicura e priva di ogni rimbalzo (bounce).

Quando si agisce su un generico circuito elettrico tramite un interruttore

a pressione manuale, l'azione meccanica avviene in tempi che rispetto alla

risposta dei circuiti logici possono essere considerati molto lunghi. Inoltre

all'avicinarsi dell'elemento mobile a quello fisso, quando la distanza tra

essi diventa esigua, viene a stabilirsi un contatto dapprima incerto che

diventa sempre più sicuro e fermo.

Durante questo intervallo di tempo, la continuità elettrica del circuito

è stabilita in modo aleatorio, attraverso una serie di rapide oscillazioni

che possono essere ritenute, dal circuito logico comandato, come altrettanti

segnali 0 ed 1 indesiderati.

L'incertezza del contatto manuale, si verifica anche durante l'apertura

dell'interruttore o il rilascio del tasto.

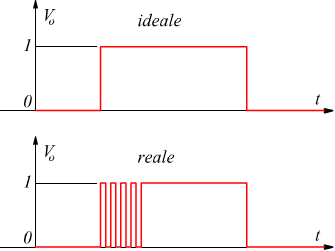

Prendiamo ad esempio il commutatore P del circuito qui disegnato; quando

P è in posizione A, Vo=0 mentre quando P è in posizione B si

ha Vo=Vcc.

Spostando P nelle due posizioni ci aspettiamo teoricamente la forma d'onda seguente:

mentre in realtà la forma d'onda rilevata, risulta caratterizzata da rimbalzi; sintomo del fatto che il contatto si interrompe più volte.

L'inconveniente si risolve interponendo, fra l'elemento meccanico e il circuito, un latch SR collegato come si vede nel seguente circuito:

Quando il commutatore è in posizione A si ha R=0,

S=1 e quindi Q=0. Si nota che i terminali A

e B, quando non sono in contatto col braccio del commutatore sono mantenuti

a Vcc e quindi a livello logico 1.

Spostando il commutatore su B si ha un primo contatto che porta S=0

ed R=1 e quindi Q=1.

Durante i successivi rimbalzi il braccio si trova a discostarsi leggermente

da B ed il latch si trova nella condizione S=1

ed R=1 cioè in uno stato di memoria.

Pertanto dopo il primo contatto, l'uscita rimane stabilmente ad 1.

In modo analogo spostando il commutatore da B ad A si ottiene sull'uscita

Q una transizione netta tra i livelli 1 e 0.

edutecnica

edutecnica