Timer 555

Si tratta di un circuito integrato per realizzare dispositivi astabili e monostabili (vedi qui). Le sue caratteristiche sono:

-Elevata stabilità del periodo di oscillazione nella gamma di frequenze

che vanno da qualche decimo di Hz a diverse centinaia di KHz.

-Tensione di alimentazione variabile da +5 a +15V

-Elevata corrente di uscita (fino a 200mA per una tensione di 15V).

-Capacità di pilotare carichi CMOS e TTL.

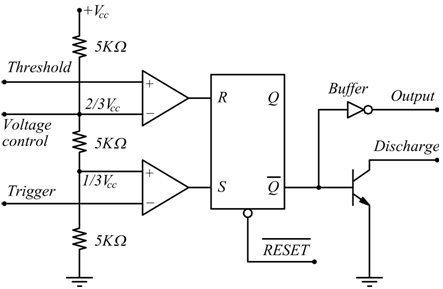

Lo schema del dispositivo è il seguente:

La tabella della verità (dove la X sèecifica una condizione di indifferenza) è la seguente:

|

Threshold |

Trigger |

Reset |

Output |

Scarica |

|

X |

X |

Basso |

Basso |

ON |

|

|

|

Alto |

Basso |

ON |

|

|

|

Alto |

STABILE |

STABILE |

|

X |

|

Alto |

Alto |

OFF |

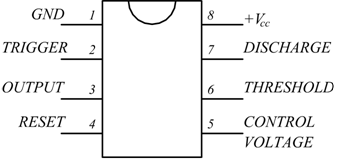

La definizione della piedinatura è la seguente:

Esso è costituito da due operazionali, usati come comparatori, da un latch SR, munito di ingresso asincrono RESET attivo basso, da un transistor e da una porta NOT.

Si notano le tre resistenze da 5K (da cui il nome 555) che funzionano da partitore resistivo, fornendo le tensioni di riferimento 2/3Vcc e 1/3Vcc ,rispettivamente al comparatore di threshold e al comparatore di trigger.

Le uscite dei due comparatori sono collegate all'ingresso del FF la cui uscita complementata comanda sia il buffer che il transistor.

I comparatori presentano in uscita un livello di tensione alto quando la tensione sull'ingresso positivo (non invertente) è maggiore di quella sull'ingresso negativo (invertente); negativo in caso contrario.

Quando la tensione all'ingresso di threshold supera i 2/3VCC

l'uscita del comparatore corrispondente e quindi l'ingresso R del latch

passa dal livello basso a quello alto, portando alta così l'uscita ![]() facendo

condurre il transistor.

facendo

condurre il transistor.

|

S |

R |

|

BJT |

|

|

|||

|

0 |

1 |

1 |

ON |

|

1 |

0 |

0 |

OFF |

Se invece la tensione all'ingresso del trigger scende al di sotto di

i 1/3VCC l'uscita del comparatore di trigger si porta alta.

L'uscita ![]() va

bassa e il transistor si interdice.

va

bassa e il transistor si interdice.

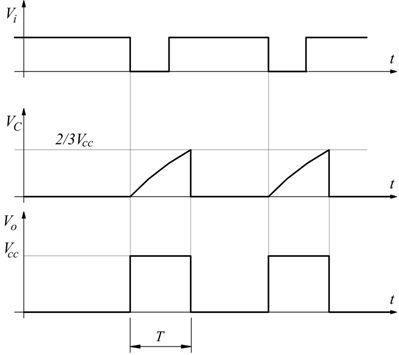

Timer 555 come dispositivo astabile

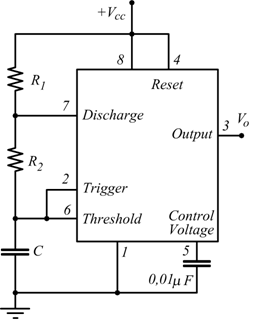

Per ottenere un funzionamento astabile il circuito va connesso così:

Quando si dà alimentazione al circuito i piedini 2 e 6 sono a potenziale

0 se il condensatore C è inizialmente scarico. Si ha S=1 ed R=0

per cui Q=1 e ![]() .

Dato che la base del BJT e l'ingresso del buffer sono collegati

a il transistor è interdetto e l'uscita

.

Dato che la base del BJT e l'ingresso del buffer sono collegati

a il transistor è interdetto e l'uscita ![]() è

alta.

è

alta.

Il condensatore tende a caricarsi alla tensione VCC attraverso

le resistenze R1 ed R2 con costante di tempo

(R1+R2)C. Quando C raggiunge il potenziale

1/3VCC il comparatore di trigger commuta portando S=R=0;

in tal caso,com'è noto, lo stato del FF non varia e C continua a

caricarsi. Raggiunto il valore 2/3VCC commuta anche il

comparatore di threshold e si ha S=0 ed R=1, il FF commuta e di

conseguenza il BJT entra in saturazione e l'uscita si porta a 0.

Tra il piedino discharge e la massa ora c'è una ddp pari a VCEsat, che in prima approssimazione vale 0. Il condensatore si scarica esclusivamente attraverso la sola R2 nel collettore del BJT.

Lo stato del FF resta immutato finché la tensione del condensatore VC resta nell'intervallo 1/3Vcc 2/3Vcc in quanto si verifica S=R=0. Quando VC scende al di sotto di 1/3Vcc si riottene S=1 R=0 per cui il BJT torna in interdizione caricando il condensatore C attraverso (R1+R2). e l'uscita si riporta a 1.

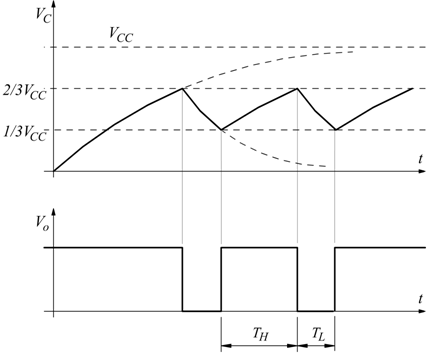

In conclusione la ddp di C oscilla tra 1/3Vcc e 2/3Vcc i e l'uscita tra 0 e VCC.

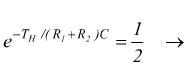

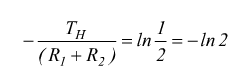

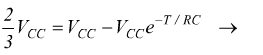

Determiniamo adesso i tempi TL e TH.

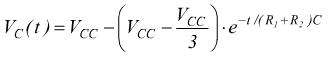

Durante la fase di carica il condensatore assume valore iniziale VCC/3 e finale VCC, cariandosi in base alla formula:

![]()

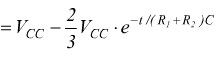

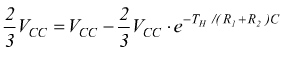

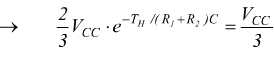

per t=TH avremo ![]()

![]()

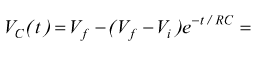

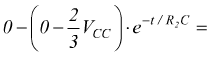

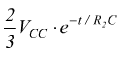

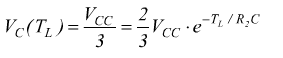

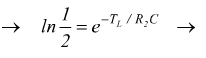

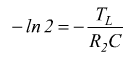

Durante la fase di scarica il condensatore assume un valore iniziale

![]() e finale 0,

ma dopo un tempo TL raggiunge il valore

e finale 0,

ma dopo un tempo TL raggiunge il valore ![]() e

commuta.

e

commuta.

poi

poi

![]() ovviamente

il periodo di oscillazione completo sarà:

ovviamente

il periodo di oscillazione completo sarà:

![]()

![]()

![]()

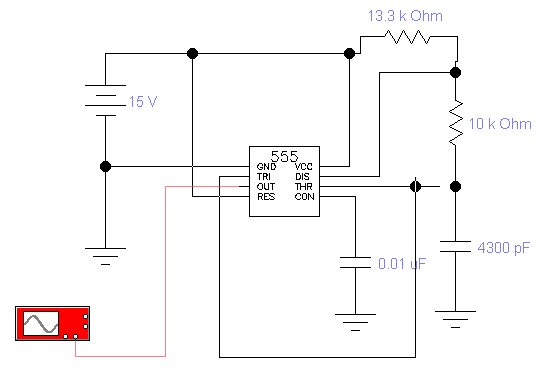

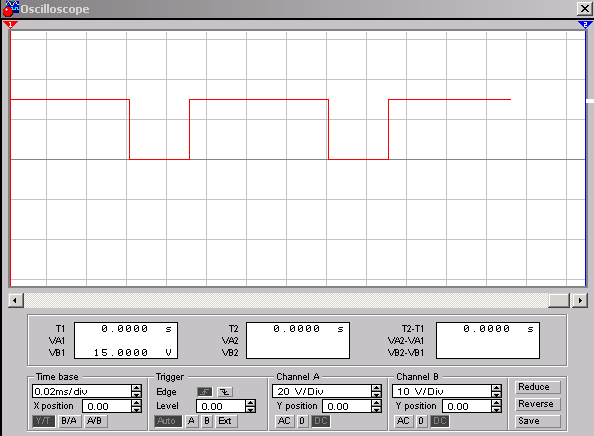

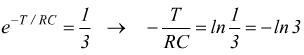

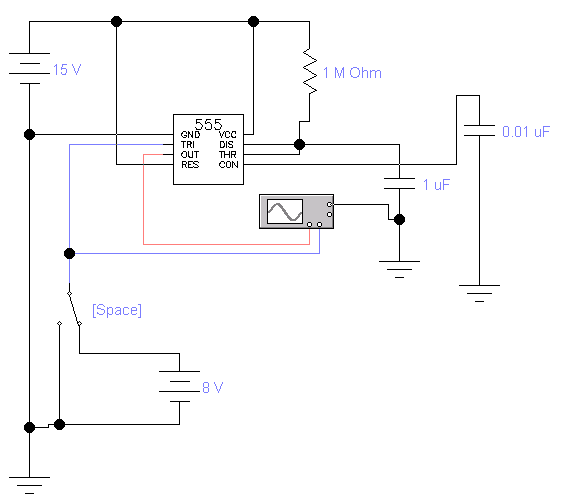

Qui di seguito indichiamo un'implementazione di un astabile realizzata al simulatore:

Timer 555 come dispositivo monostabile

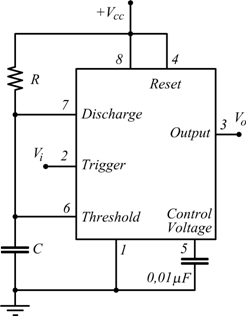

Per ottenere un funzionamento monostabile può essere fatta una connessione così:

In condizioni normali l'ingresso positivo del comparatore di threshold

è tenuto al potenziale +VCC tramite la resistenza R mentre

l'ingresso negativo è a 2/3VCC. In questo caso essendo

V+>V- l'ingresso R e di conseguenza l'uscita

![]() sono

alti.

sono

alti.

L'ingresso di trigger è invece tenuto ad un potenziale maggiore di 1/3VCC mediante la scelta di un opportuno valore di R così essendo V->V+ l'uscita del secondo comparatore viene fissata a livello basso S=0.

In questa situazione con R=1 ed S=0 il transistor risulta in forte conduzione ed il condensatore C è scarico.

Non appena viene inviato all'ingresso di trigger un impulso negativo di ampiezza inferiore a 1/3VCC l'uscita del comparatore di trigger passa ad un livello alto, l'uscita del FF va bassa e il transistor si interdice.

Il condensatore allora inizia a caricarsi attraverso la resistenza R collegata all'alimentazione, ma dato che la tensione ai capi del condensatore è applicata all'ingresso di threshold, non appena essa raggiunge il valore 2/3VCC l'uscita del comparatore passa a livello alto e il transistor viene portato in conduzione; il condensatore si scarica, quindi, rapidamente tramite attraverso la bassa resistenza di uscita del BJT e resta scarico fino all'arrivo di un nuovo impulso.

Durante il tempo in cui l'uscita del monostabile è alta, l'applicazione di ulteriori impulsi all'ingresso di trigger non sortiscono nessun effetto.

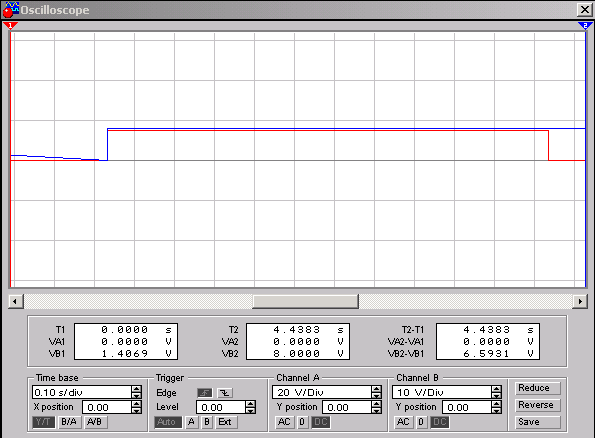

Durante la carica il condensatore tenderà a caricarsi alla tensione VCC.

![]()

durante questa fase di carica raggiunge il valore 2/3VCC dopo un tempo T, per cui l'equazione precedente diventa:

per

cui :

per

cui :

![]()

Qui di seguito è riportata un'implementazione di un monostabile realizzata al simulatore:

edutecnica

edutecnica